Physical Address

304 North Cardinal St.

Dorchester Center, MA 02124

Physical Address

304 North Cardinal St.

Dorchester Center, MA 02124

Системные программисты с незапамятных времен любят обсуждать извечный философский вопрос: как двум процессам лучше всего наладить взаимодействие? И можно ли в каких-то случаях избежать ненужного посредника в виде операционной системы? Оказывается, это вполне реально: достаточно только спуститься на уровень ниже, к аппаратной части, и поискать решение среди векторных регистров процессора.

Сегодняшний рассказ о найденном внутри набора команд сюрпризе был бы неполным без краткой предыстории. Впервые векторные регистры у компании Intel появились в процессорах Pentium MMX (MultiMedia eXtensions) в 1997 году. Сегодня их ширина (64 бит) выглядит вполне стандартной, но более чем двадцать лет назад так, конечно, никто не считал.

В самой компании новыми инструкциями SIMD (Single Instruction, Multiple Data) очень гордились, и было решено даже посвятить их популяризации целый номер Intel Technology Journal.

Направление развития и впрямь оказалось удачным, и уже через два года вместе с анонсом Pentium III архитектура набора команд пополнилась технологией SSE (Streaming SIMD Extensions, 128 бит). C появлением улучшений и новых версий эта технология просуществовала до выхода Sandy Bridge с AVX (Advanced Vector Extensions, 256 бит) в 2011 году.

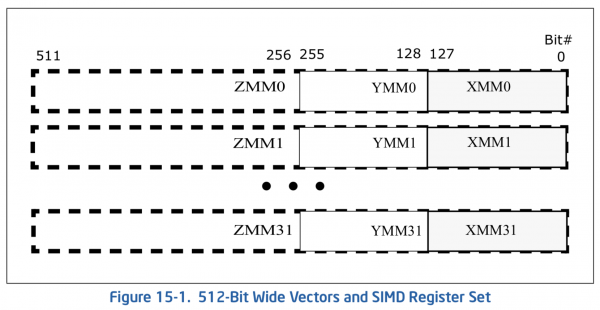

В более новых архитектурах компания Intel пошла еще дальше, дополнив набор ISA (Instruction Set Architecture) группой расширений AVX2 (Haswell, 2013). Вполне вероятно, что именно их поддерживает твой нынешний процессор. Впрочем, если ты предпочитаешь серверные решения, то начиная с Knights Landing (2016) специально для тебя существует набор AVX-512 (с угадай какой шириной регистров).

В графическом виде развитие принципа SIMD применительно к процессорам Intel выглядит так

Предыдущая картинка призвана навести тебя на простую мысль: регистры у нас большие и регистров у нас много. А раз так, операции со значениями в таких регистрах должны потреблять больше энергии, попутно преобразовывая ее в тепло (которое предстоит еще как-то отвести от кристалла процессора).

Более того, даже просто поддерживать регистры SIMD в активном состоянии весьма расточительно с точки зрения энергозатрат. Поэтому Skylake и более поздние архитектуры активируют их только по мере необходимости. Если процессор работает в скалярном режиме, крупноразмерные регистры находятся в деактивированном состоянии.

Процессор пробуждает векторные регистры только в том случае, если какое-нибудь ядро натыкается на инструкции SIMD в коде. Однако процесс перевода регистров в активное состояние — дело небыстрое.

Поэтому в тот промежуток времени, когда потребность в крупноразмерных регистрах уже возникла, но «проснуться» они еще не успели, векторный код обрабатывается микрокодом, который оперирует более короткими регистрами и, следовательно, работает примерно на половине скорости.

С другой стороны, после того как цепочка векторных команд заканчивается и потребность в крупноразмерных регистрах отпадает, обрабатывающее их ядро снова деактивирует эти регистры. И опять-таки не сразу — на случай, если поблизости окажутся еще какие-нибудь векторные команды.

На первый взгляд это все может показаться совершенно излишним, но попытаемся разобраться во внутренней логике и мотивах инженеров компании Intel.

Что же в действительности происходит, когда у какого-нибудь ядра, обнаружившего векторную команду, возникает потребность в получении дополнительной электроэнергии для работы с AVX? Оказывается, оно не может самостоятельно выделить себе необходимые амперы — для этого требуется получить разрешение у PCU (Package Control Unit).

По сути, это такой встроенный микроконтроллер, который регулирует тактовые частоты и напряжение питания процессора. Помимо прочего, он следит за температурой самого кристалла и при критических значениях уводит ядро в режим тротлинга, чтобы не возникало перегрева.

Таким образом, решение о подаче дополнительного питания принимает исключительно PCU, руководствуясь собственными правилами и текущей ситуацией. В документации Intel такой процесс называется выдачей лицензии на электроэнергию.

При этом ядру может быть предоставлено несколько видов лицензии, в зависимости от типа команд, которые оно собирается выполнять. Для всех базовых инструкций AVX и некоторых простых инструкций AVX2 (загрузка или сложение) ядру выписывается номинальная лицензия LVL0_TURBO_LICENSE. На обработку сложных команд AVX2 PCU выдает лицензию серьезней: LVL1_TURBO_LICENSE.

А уж если какому-нибудь ядру посчастливилось наткнуться на AVX-512, то ему предоставляется лицензия премиум-класса — LVL2_TURBO_LICENSE. Однако при этом ядро процессора оказывается ограниченным не только в питании, но и в максимальной тактовой частоте.

В спецификациях Intel это упоминается как минимальная гарантируемая частота (AVX Turbo) для ситуации, когда все ядра процессора оказались полностью загружены обработкой инструкций SIMD.

Рассмотрим реальный пример и попытаемся понять, к чему это все приводит на практике. Максимальная частота серверного процессора Intel Xeon Gold 6130 для скалярных инструкций составляет 2,8 ГГц. Если нагрузить его векторными инструкциями из числа базовых, максимальная частота уже упадет до 2,4 ГГц. Наиболее же серьезным испытанием станут как раз команды из набора AVX-512, заботами PCU частота при этом не превысит 1,9 ГГц.

Источник: xakep.ru